A complexidade da montagem de placas de circuito impresso (PCBA) está crescendo, assim como a necessidade de testes para garantir qualidade, confiabilidade e funcionalidade na área de fabricação de eletrônicos.

À medida que continuamos a ultrapassar os limites do que é possível com a eletrónica, a procura por sistemas eletrónicos fiáveis e de alto desempenho continua a crescer. Como resultado, a complexidade da montagem de placas de circuito impresso (PCBA) está aumentando, assim como a necessidade de testes para garantir qualidade, confiabilidade e funcionalidade na área de fabricação de eletrônicos.

Desafio nº 1: Aumentar a densidade de PCBA e a demanda de alto volume na fabricação

À medida que o progresso tecnológico avança, houve uma mudança significativa no desejo por dispositivos compactos e com design complexo. Isto desencadeou uma evolução significativa no design do PCBA, caracterizado por dois desenvolvimentos principais:

Miniaturização de dispositivos, em resposta à crescente demanda por tudo menor e mais rápido. Como resultado, os projetistas estão aumentando ativamente a funcionalidade do PCBA, aumentando assim o número de componentes que requerem acesso para teste.

Há um grande volume de PCBA e, embora o aumento no acesso ao teste seja inevitável, esse crescimento do volume criou um gargalo nos sistemas de teste em circuito (ICT).

Enfrentar esses desafios significa aproveitar a tecnologia que pode acomodar mais nós de teste. Em última análise, isto significa aumentar a capacidade e permitir o processamento de painéis maiores.

Desafio nº 2: teste curto mais longo em nó de alta impedância

Um teste curto é um teste padrão sem motorização realizado durante as TIC. Este teste verifica curtos-circuitos indesejados entre componentes em um PCBA. O teste curto também ajuda a proteger a placa contra danos na fase subsequente de testes energizados. À medida que a tecnologia evolui, a prevalência de nós de alta impedância tem aumentado, impulsionada pela crescente procura de qualidade de sinal, menor consumo de energia e melhor funcionalidade.

No entanto, a curta duração do teste para o nó de alta impedância é notavelmente mais longa. Em média, leva três vezes mais tempo para testar um nó de alta impedância em comparação com um nó de baixa impedância. Essa discrepância nos testes surge devido às características únicas dos nós de alta impedância, que requerem maior tempo de estabilização devido ao baixo fluxo de corrente, e como pequenas quantidades de ruído podem afetar as medições. Portanto, os testadores devem aplicar o sinal de teste por um período prolongado para estabilizar a tensão ou corrente e garantir leituras precisas. Também há complexidade durante o isolamento de curto quando um curto é detectado em um nó de alta impedância. Isolar e identificar os nós específicos em curto pode ser um processo mais complexo. Este tempo de teste prolongado pode potencialmente impedir o rendimento geral dos testes da linha de produção, colocando desafios à eficiência e à velocidade de produção.

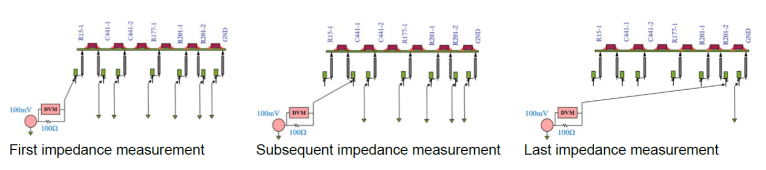

Enfrentando os desafios associados ao teste de nós de alta impedância, o teste curto aprimorado compreende duas fases: uma fase de detecção e uma fase de isolamento. Projetado especificamente para aumentar a eficiência da detecção de curtos para nós de alta impedância, este novo algoritmo não é aplicável a nós de baixa impedância ou nós com curtos conhecidos.

![1]()

Figura 1: Nós de alta impedância são divididos em grupos usando o ID binário e medidos quanto à resistência para verificar curtos.

Considere um cenário onde uma placa contém 100 nós de alta impedância. Neste caso, cada nó terá um comprimento de identificador de 7 bits. Através da implementação do teste curto aprimorado, o processo de teste foi significativamente simplificado, exigindo apenas sete iterações para concluir o teste, em vez de 100. Consequentemente, esta redução no número de iterações minimiza efetivamente a duração geral do teste.

Durante a fase de isolamento, se um curto-circuito for detectado, o método de teste de curto-circuito aprimorado emprega a técnica de redução pela metade para identificar os nós específicos onde ocorreu o curto-circuito inesperado, espelhando o algoritmo padrão. No entanto, uma distinção fundamental está na sequência: os nós em curto são inicialmente identificados de um grupo e posteriormente do outro, otimizando a eficiência do processo de identificação.

Desafios nº 3: Testando supercapacitores (1 a 100 Farads) em testes em circuito

Supercapacitores, muitas vezes chamados de SuperCaps, são um tipo de capacitor caracterizado por sua alta capacitância, variando de 1 farad a 100 farads. Os capacitores, em geral, são dispositivos eletroquímicos projetados para armazenar energia na forma de energia eletrostática.

A excepcional capacidade de armazenamento de energia dos supercapacitores os torna particularmente valiosos em diversas aplicações, como no suporte a veículos elétricos e híbridos (EVs/HEVs) e veículos elétricos híbridos plug-in (PHEVs). Eles são utilizados para funcionalidade stop-start, aceleração rápida e operações de frenagem regenerativa.

Além de suas aplicações automotivas, os supercapacitores servem como fonte de energia secundária, fornecendo energia de reserva de emergência para sistemas críticos em caso de falha ou durante procedimentos de inicialização. Além disso, desempenham um papel crucial na manutenção de níveis de tensão estáveis no sistema eléctrico de um veículo, melhorando assim a qualidade da energia. Essa estabilidade garante que os componentes eletrônicos sensíveis recebam uma fonte de alimentação consistente e confiável, contribuindo para a confiabilidade e o desempenho geral do sistema.

Portanto, é essencial carregar, testar e descarregar supercapacitores com precisão.

![Figura 2: Conexão de teste SuperCap]()

Figura 2: Conexão de teste SuperCap

Desafio nº 4: Medições de baixa corrente em testes em circuito

As correntes de fuga e de sono desempenham um papel crucial no desempenho de vários dispositivos, incluindo dispositivos móveis, equipamentos médicos e unidades automotivas. Estas correntes são indicadores particularmente significativos do consumo de energia de um dispositivo, fornecendo informações sobre quanto tempo a bateria pode sustentar a operação antes de necessitar de recarga ou substituição.

Em aplicações automotivas, as unidades de controle do motor (ECUs) exemplificam a importância do gerenciamento de correntes de fuga e de suspensão. As ECUs supervisionam funções críticas na operação de um motor, como controle climático, gerenciamento de airbags e sistemas de freios antibloqueio. O manuseio ineficiente dessas correntes dentro das ECUs pode resultar em um consumo desnecessário da bateria, levando à redução da vida útil da bateria e a possíveis problemas elétricos.

Além das preocupações com a eficiência, as correntes de fuga também representam um risco significativo à segurança. O mau funcionamento induzido por essas correntes pode fazer com que os circuitos críticos de segurança dentro das ECUs se comportem de maneira imprevisível, resultando potencialmente em situações perigosas. Por exemplo, o mau funcionamento dos sistemas de segurança pode levar à falha no acionamento dos airbags durante uma colisão. Considerando esses riscos potenciais, medições meticulosas de baixa corrente são imperativas.

Desafio nº 5: Acesso limitado ao teste no PCBA

Alcançar testes abrangentes de um PCBA de alta densidade requer que pontos de teste sejam posicionados em cada nó elétrico em todo o circuito, permitindo que o testador no circuito execute testes completos de componentes e conexões. No entanto, acomodar pontos de teste em todos os nós elétricos dentro de um PCBA densamente compactado é impraticável. Esta limitação na alocação de pontos de teste leva a uma diminuição na cobertura de teste para um PCBA de alta densidade.

Isso pode ser resolvido introduzindo a formação automatizada de clusters e a geração de testes para esses clusters. Um recurso automatizado calcula a impedância equivalente do cluster analógico passivo e a compara com os resultados da medição. Posteriormente, criar um plano de teste abrangente adaptado para medir componentes de cluster em PCBAs densamente compactados. Isso reduz significativamente o esforço de engenharia necessário para identificar clusters manualmente e gerar testes.

![Figura 3: Tipos de dispositivos e quais dispositivos são aceitos para teste de cluster.]()

Figura 3: Tipos de dispositivos e quais dispositivos são aceitos para teste de cluster.

O algoritmo aprimorado de teste de cluster é introduzido no testador de circuito de alta densidade e apresenta uma solução automatizada para criar clusters de dispositivos passivos confiáveis e gerar planos de teste. Aproveitar o poder de um algoritmo da biblioteca avançada de cluster (ACL) garante a formação eficiente de cluster. Os estágios subsequentes envolvem validação rigorosa de requisitos de hardware, contribuindo para identificar clusters confiáveis para fins de teste. Ao simplificar o processo, até mesmo engenheiros de teste novatos podem executar testes com eficácia. Esse avanço permite que os clientes desfrutem de maior precisão de testes, execução de testes mais rápida e maior confiabilidade em seus processos de produção, tudo facilitado pelo algoritmo de teste de cluster automatizado.

Resumo

Para enfrentar os desafios atuais dos testes de PCBA, é essencial reduzir o número de iterações, diminuindo consequentemente a duração dos testes necessária para PCBAs de alta densidade. Ao permitir tempos de teste mais rápidos e reimaginar a cobertura dos testes, os fabricantes serão capazes de superar as complexidades.

Fonte de: EE Times