La complexité de l'assemblage de cartes de circuits imprimés (PCBA) augmente, tout comme le besoin de tests pour garantir la qualité, la fiabilité et la fonctionnalité dans le secteur de la fabrication électronique.

Alors que nous continuons à repousser les limites de ce qui est possible avec l'électronique, la demande de systèmes électroniques fiables et performants continue de croître. En conséquence, la complexité de l'assemblage de cartes de circuits imprimés (PCBA) augmente, tout comme le besoin de tests pour garantir la qualité, la fiabilité et la fonctionnalité dans les ateliers de fabrication électronique.

Défi n°1 : Augmentation de la densité des PCBA et de la demande élevée dans le secteur manufacturier

À mesure que les progrès technologiques progressent, il y a eu un changement significatif dans le désir d'appareils compacts et de conception complexe. Cela a déclenché une évolution significative dans la conception des PCBA, caractérisée par deux développements clés :

Miniaturisation des appareils, en réponse à la demande croissante de tout ce qui est plus petit et plus rapide. En conséquence, les concepteurs augmentent activement les fonctionnalités du PCBA, augmentant ainsi le nombre de composants nécessitant un accès aux tests.

Il existe un volume élevé de PCBA et, bien que l'augmentation de l'accès aux tests soit inévitable, cette croissance du volume a créé un goulot d'étranglement dans les systèmes de test en circuit (TIC).

Pour relever ces défis, il faut tirer parti d’une technologie capable de prendre en charge davantage de nœuds de test. Cela signifie à terme augmenter la capacité et permettre le traitement de panneaux plus grands.

Défi n°2 : test plus court sur un nœud haute impédance

Un test court est un test standard non alimenté effectué pendant les TIC. Ce test vérifie les courts-circuits indésirables entre les composants d'un PCBA. Le test court permet également de protéger la carte contre les dommages lors de la phase de tests sous tension ultérieure. À mesure que la technologie évolue, la prévalence des nœuds à haute impédance augmente, en raison de la demande croissante de qualité de signal, de consommation d'énergie réduite et de fonctionnalités améliorées.

Cependant, la courte durée du test pour le nœud à haute impédance est nettement plus longue. En moyenne, il faut trois fois plus de temps pour tester un nœud à haute impédance qu’un nœud à faible impédance. Cet écart dans les tests est dû aux caractéristiques uniques des nœuds à haute impédance, qui nécessitent un temps de stabilisation plus long en raison du faible flux de courant, et à la manière dont de petites quantités de bruit peuvent affecter les mesures. Par conséquent, les testeurs doivent appliquer le signal de test pendant une période prolongée pour stabiliser la tension ou le courant afin de garantir des lectures précises. L'isolation courte présente également une certaine complexité lorsqu'un court-circuit est détecté sur un nœud à haute impédance. L'isolation et l'identification des nœuds court-circuités spécifiques peuvent être un processus plus complexe. Cette durée de test prolongée pourrait potentiellement entraver le débit global des tests de la chaîne de fabrication, posant ainsi des problèmes d'efficacité et de vitesse de production.

Répondant aux défis associés au test des nœuds à haute impédance, le test court amélioré comprend deux phases : une phase de détection et une phase d'isolement. Spécialement conçu pour améliorer l'efficacité de la détection des courts-circuits pour les nœuds à haute impédance, ce nouvel algorithme n'est pas applicable aux nœuds à faible impédance ou aux nœuds avec des courts-circuits connus.

![1]()

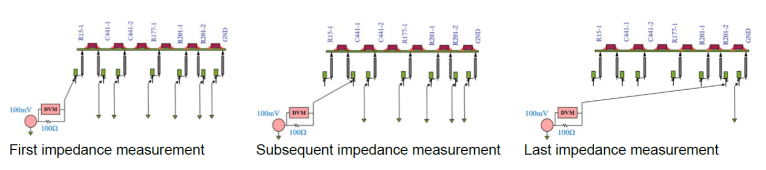

Figure 1 : Les nœuds à haute impédance sont divisés en groupes à l'aide de l'ID binaire et leur résistance est mesurée afin de détecter les courts-circuits.

Prenons un scénario dans lequel une carte contient 100 nœuds à haute impédance. Dans ce cas, chaque nœud aura une longueur d'identifiant de 7 bits. Grâce à la mise en œuvre du test court amélioré, le processus de test a été considérablement rationalisé, ne nécessitant que sept itérations pour terminer le test au lieu de 100. Par conséquent, cette réduction du nombre d'itérations minimise efficacement la durée globale du test.

Pendant la phase d'isolement, si un court-circuit est détecté, la méthode de test de court-circuit améliorée utilise la technique de réduction de moitié pour identifier les nœuds spécifiques où le court-circuit inattendu s'est produit, reflétant l'algorithme standard. Cependant, une distinction clé réside dans la séquence : les nœuds court-circuités sont initialement identifiés dans un groupe, puis dans l'autre, optimisant ainsi l'efficacité du processus d'identification.

Défis n°3 : Tester des supercondensateurs (1 à 100 Farads) lors de tests en circuit

Les supercondensateurs, souvent appelés SuperCaps, sont un type de condensateurs caractérisés par leur capacité élevée, allant de 1 farad à 100 farads. Les condensateurs, en général, sont des dispositifs électrochimiques conçus pour stocker de l'énergie sous forme d'énergie électrostatique.

La capacité exceptionnelle de stockage d'énergie des supercondensateurs les rend particulièrement utiles dans un certain nombre d'applications, telles que le support des véhicules électriques et hybrides (VE/HEV) et des véhicules électriques hybrides rechargeables (PHEV). Ils sont utilisés pour la fonctionnalité arrêt-démarrage, les opérations d’accélération rapide et de freinage par récupération.

En plus de leurs applications automobiles, les supercondensateurs servent de source d'alimentation secondaire, fournissant une alimentation de secours aux systèmes critiques en cas de panne ou pendant les procédures de démarrage. De plus, ils jouent un rôle crucial dans le maintien de niveaux de tension stables au sein du système électrique d'un véhicule, améliorant ainsi la qualité de l'énergie. Cette stabilité garantit que les composants électroniques sensibles reçoivent une alimentation électrique constante et fiable, contribuant ainsi à la fiabilité et aux performances globales du système.

Il est donc essentiel de charger, tester et décharger les supercondensateurs avec précision.

![Figure 2 : connexion de test SuperCap]()

Figure 2 : connexion de test SuperCap

Défi n°4 : Mesures de faible courant dans les tests en circuit

Les courants de fuite et de sommeil jouent un rôle crucial dans les performances de divers appareils, notamment les appareils mobiles, les équipements médicaux et les unités automobiles. Ces courants sont des indicateurs particulièrement significatifs de la consommation d'énergie d'un appareil, fournissant des informations sur la durée pendant laquelle la batterie peut fonctionner avant de devoir être rechargée ou remplacée.

Dans les applications automobiles, les unités de commande moteur (ECU) illustrent l'importance de la gestion des courants de fuite et de sommeil. Les calculateurs supervisent les fonctions critiques du fonctionnement d'un moteur, telles que la climatisation, la gestion des airbags et les systèmes de freinage antiblocage. Une gestion inefficace de ces courants dans les calculateurs peut entraîner une décharge inutile de la batterie, entraînant une durée de vie réduite de la batterie et des dysfonctionnements électriques potentiels.

Au-delà des problèmes d’efficacité, les courants de fuite posent également un risque important pour la sécurité. Les dysfonctionnements induits par ces courants peuvent entraîner un comportement imprévisible des circuits critiques pour la sécurité au sein des calculateurs, entraînant potentiellement des situations dangereuses. Par exemple, un dysfonctionnement des systèmes de sécurité pourrait entraîner l’échec du déploiement des airbags lors d’une collision. Compte tenu de ces risques potentiels, des mesures méticuleuses à faible courant sont impératives.

Défi n°5 : Accès limité aux tests sur PCBA

La réalisation de tests complets d'un PCBA haute densité nécessite que des points de test soient positionnés sur chaque nœud électrique du circuit, permettant au testeur en circuit d'effectuer des tests approfondis de composants et de connexions. Cependant, il n'est pas pratique de placer des points de test sur tous les nœuds électriques dans une PCBA densément peuplée. Cette limitation dans l'attribution des points de test entraîne une diminution de la couverture des tests pour un PCBA haute densité.

Ce problème peut être résolu en introduisant la formation automatisée de clusters et la génération de tests pour ces clusters. Une fonction automatisée calcule l'impédance équivalente du cluster analogique passif et la compare aux résultats de mesure. Par la suite, création d'un plan de test complet adapté à la mesure des composants de cluster sur des PCBA densément emballés. Cela réduit considérablement les efforts d'ingénierie requis pour identifier manuellement les clusters et générer des tests.

![Figure 3 : Types d'appareils et quels appareils sont acceptés pour le test de cluster.]()

Figure 3 : Types d'appareils et quels appareils sont acceptés pour le test de cluster.

L'algorithme de test de cluster amélioré est introduit dans le testeur en circuit haute densité et présente une solution automatisée pour créer des clusters de dispositifs passifs fiables et générer des plans de test. Tirer parti de la puissance d’un algorithme de la bibliothèque de clusters avancée (ACL) garantit une formation efficace des clusters. Les étapes suivantes impliquent une validation rigoureuse des exigences matérielles, contribuant à identifier des clusters fiables à des fins de test. En rationalisant le processus, même les ingénieurs de test novices peuvent exécuter efficacement des tests. Cette avancée permet aux clients de bénéficier d'une précision de test améliorée, d'une exécution plus rapide des tests et d'une fiabilité accrue dans leurs processus de production, le tout facilité par l'algorithme de test de cluster automatisé.

Résumé

Pour relever les défis actuels des tests PCBA, il est essentiel de réduire le nombre d'itérations, réduisant ainsi la durée des tests requis pour les PCBA haute densité. En permettant des temps de test plus rapides et en réinventant la couverture des tests, les fabricants seront en mesure de surmonter les complexités.

Source de : EE Times