La complejidad del ensamblaje de placas de circuito impreso (PCBA) está creciendo y también lo está la necesidad de realizar pruebas para garantizar la calidad, confiabilidad y funcionalidad en la planta de fabricación electrónica.

A medida que continuamos superando los límites de lo que es posible con la electrónica, la demanda de sistemas electrónicos confiables y de alto rendimiento continúa creciendo. Como resultado, la complejidad del ensamblaje de placas de circuito impreso (PCBA) está creciendo y también la necesidad de realizar pruebas para garantizar la calidad, confiabilidad y funcionalidad en la planta de fabricación electrónica.

Desafío n.º 1: aumento de la densidad de PCBA y demanda de gran volumen en la fabricación

A medida que avanza el progreso tecnológico, ha habido un cambio significativo en el deseo de dispositivos compactos y de diseño intrincado. Esto ha provocado una evolución significativa en el diseño de PCBA, caracterizada por dos desarrollos clave:

Miniaturización de dispositivos, como respuesta a la creciente demanda de todo lo más pequeño y rápido. Como resultado, los diseñadores están aumentando activamente la funcionalidad de la PCBA, aumentando así la cantidad de componentes que requieren acceso de prueba.

Existe un gran volumen de PCBA y, si bien el aumento del acceso a las pruebas es inevitable, este crecimiento del volumen ha creado un cuello de botella en los sistemas de pruebas en circuito (TIC).

Abordar estos desafíos significa aprovechar la tecnología que pueda acomodar más nodos de prueba. En última instancia, esto significa aumentar la capacidad y permitir procesar paneles más grandes.

Desafío #2: Prueba corta más larga en un nodo de alta impedancia

Una prueba corta es una prueba estándar sin alimentación que se realiza durante las TIC. Esta prueba busca cortocircuitos no deseados entre componentes en una PCBA. La prueba breve también ayuda a proteger la placa de daños en la fase posterior de pruebas eléctricas. A medida que la tecnología evoluciona, la prevalencia de nodos de alta impedancia ha aumentado, impulsada por la creciente demanda de calidad de señal, menor consumo de energía y funcionalidad mejorada.

Sin embargo, la duración corta de la prueba para el nodo de alta impedancia es notablemente mayor. En promedio, se tarda tres veces más en probar un nodo de alta impedancia que uno de baja impedancia. Esta discrepancia en las pruebas surge debido a las características únicas de los nodos de alta impedancia, que requieren un tiempo de estabilización más prolongado debido al bajo flujo de corriente, y a cómo pequeñas cantidades de ruido pueden afectar las mediciones. Por lo tanto, los probadores deben aplicar la señal de prueba durante un período prolongado para estabilizar el voltaje o la corriente y garantizar lecturas precisas. También existe complejidad durante el aislamiento corto, cuando se detecta un cortocircuito en un nodo de alta impedancia; aislar e identificar los nodos en corto específicos puede ser un proceso más complejo. Este tiempo de prueba prolongado podría potencialmente impedir el rendimiento general de las pruebas de la línea de fabricación, planteando desafíos a la eficiencia y la velocidad de producción.

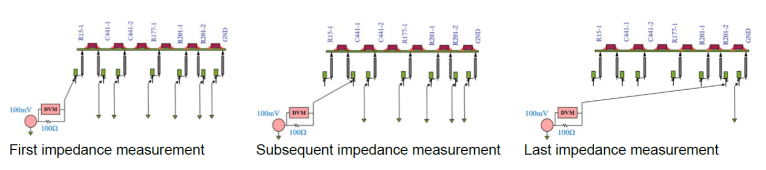

La prueba corta mejorada, que aborda los desafíos asociados con las pruebas de nodos de alta impedancia, consta de dos fases: una fase de detección y una fase de aislamiento. Diseñado específicamente para mejorar la eficiencia de la detección de cortocircuitos en nodos de alta impedancia, este nuevo algoritmo no es aplicable a nodos de baja impedancia o nodos con cortocircuitos conocidos.

![1]()

Figura 1: Los nodos de alta impedancia se dividen en grupos utilizando la identificación binaria y se mide su resistencia para verificar si hay cortocircuitos.

Considere un escenario en el que una placa contiene 100 nodos de alta impedancia. En este caso, cada nodo tendrá una longitud de identificador de 7 bits. Mediante la implementación de la prueba corta mejorada, el proceso de prueba se simplificó significativamente, requiriendo solo siete iteraciones para completar la prueba en lugar de 100. En consecuencia, esta reducción en el número de iteraciones minimiza efectivamente la duración general de la prueba.

Durante la fase de aislamiento, si se detecta un cortocircuito, el método de prueba de cortocircuito mejorado emplea la técnica de reducción a la mitad para identificar los nodos específicos donde ocurrió el cortocircuito inesperado, reflejando el algoritmo estándar. Sin embargo, una distinción clave reside en la secuencia: los nodos en cortocircuito se identifican inicialmente de un grupo y posteriormente del otro, optimizando la eficiencia del proceso de identificación.

Desafíos n.º 3: probar supercondensadores (de 1 a 100 faradios) en pruebas en circuito

Los supercondensadores, a menudo denominados SuperCaps, son un tipo de condensadores que se caracterizan por su alta capacitancia, que oscila entre 1 faradio y 100 faradios. Los condensadores, en general, son dispositivos electroquímicos diseñados para almacenar energía en forma de energía electrostática.

La excepcional capacidad de almacenamiento de energía de los supercondensadores los hace particularmente valiosos en una serie de aplicaciones, como el soporte de vehículos eléctricos e híbridos (EV/HEV) y vehículos eléctricos híbridos enchufables (PHEV). Se utilizan para funciones de parada y arranque, aceleración rápida y operaciones de frenado regenerativo.

Además de sus aplicaciones automotrices, los supercondensadores sirven como fuente de energía secundaria, proporcionando energía de respaldo de emergencia a sistemas críticos en caso de falla o durante los procedimientos de arranque. Además, desempeñan un papel crucial en el mantenimiento de niveles de voltaje estables dentro del sistema eléctrico de un vehículo, mejorando así la calidad de la energía. Esta estabilidad garantiza que los componentes electrónicos sensibles reciban un suministro de energía consistente y confiable, lo que contribuye a la confiabilidad y el rendimiento general del sistema.

Por tanto, es fundamental cargar, probar y descargar supercondensadores con precisión.

![Figura 2: Conexión de prueba SuperCap]()

Figura 2: Conexión de prueba SuperCap

Desafío n.º 4: mediciones de baja corriente en pruebas en circuito

Las corrientes de fuga y de sueño desempeñan un papel crucial en el rendimiento de diversos dispositivos, incluidos dispositivos móviles, equipos médicos y unidades automotrices. Estas corrientes son indicadores particularmente significativos del consumo de energía de un dispositivo, ya que brindan información sobre cuánto tiempo la batería puede mantenerse en funcionamiento antes de que sea necesario recargarla o reemplazarla.

En aplicaciones automotrices, las unidades de control del motor (ECU) ejemplifican la importancia de gestionar las corrientes de fuga y de reposo. Las ECU supervisan funciones críticas dentro del funcionamiento de un motor, como el control del clima, la gestión de las bolsas de aire y los sistemas de frenos antibloqueo. El manejo ineficiente de estas corrientes dentro de las ECU puede provocar un consumo innecesario de la batería, lo que acorta su vida útil y posibles fallos eléctricos.

Más allá de las preocupaciones sobre la eficiencia, las corrientes de fuga también suponen un importante riesgo para la seguridad. Las fallas inducidas por estas corrientes pueden causar que los circuitos críticos para la seguridad dentro de las ECU se comporten de manera impredecible, lo que podría generar situaciones peligrosas. Por ejemplo, un mal funcionamiento de los sistemas de seguridad podría provocar que no se desplieguen los airbags durante una colisión. Teniendo en cuenta estos riesgos potenciales, es imprescindible realizar mediciones meticulosas de baja corriente.

Desafío n.º 5: acceso limitado a pruebas en PCBA

Lograr pruebas integrales de una PCBA de alta densidad requiere que se coloquen puntos de prueba en cada nodo eléctrico en todo el circuito, lo que permite que el probador en el circuito realice pruebas exhaustivas de componentes y conexiones. Sin embargo, no es práctico acomodar puntos de prueba en todos los nodos eléctricos dentro de una PCBA densamente empaquetada. Esta limitación en la asignación de puntos de prueba conduce a una disminución en la cobertura de pruebas para una PCBA de alta densidad.

Esto se puede solucionar introduciendo la formación automatizada de grupos y la generación de pruebas para estos grupos. Una función automatizada calcula la impedancia equivalente del grupo analógico pasivo y la compara con los resultados de las mediciones. Posteriormente, se creó un plan de prueba integral diseñado para medir componentes del grupo en PCBA densamente empaquetados. Esto reduce significativamente el esfuerzo de ingeniería necesario para identificar manualmente los clústeres y generar pruebas.

![Figura 3: Tipos de dispositivos y qué dispositivos se aceptan para la prueba de clúster.]()

Figura 3: Tipos de dispositivos y qué dispositivos se aceptan para la prueba de clúster.

El algoritmo de prueba de clúster mejorado se introduce en el probador en circuito de alta densidad y presenta una solución automatizada para crear clústeres de dispositivos pasivos confiables y generar planes de prueba. Aprovechar el poder de un algoritmo de la biblioteca de clústeres avanzada (ACL) garantiza una formación de clústeres eficiente. Las etapas posteriores implican una estricta validación de los requisitos de hardware, lo que contribuye a identificar clústeres confiables con fines de prueba. Al simplificar el proceso, incluso los ingenieros de pruebas novatos pueden ejecutar pruebas de manera efectiva. Este avance tiene el potencial de que los clientes disfruten de una precisión de prueba mejorada, una ejecución de prueba más rápida y una confiabilidad mejorada en sus procesos de producción, todo facilitado por el algoritmo de prueba de clúster automatizado.

Resumen

Para abordar los desafíos actuales de las pruebas de PCBA, es esencial reducir el número de iteraciones y, en consecuencia, disminuir la duración de las pruebas requeridas para los PCBA de alta densidad. Al permitir tiempos de prueba más rápidos y reinventar la cobertura de las pruebas, los fabricantes podrán superar las complejidades.

Fuente de: EE Times